Name: Dr. Deepak Sharma

**Topic:** Computer Organization

Subtopic No.1: CPU

**Keywords:** CU, ALU, memory, registers

## 1.0 CPU:

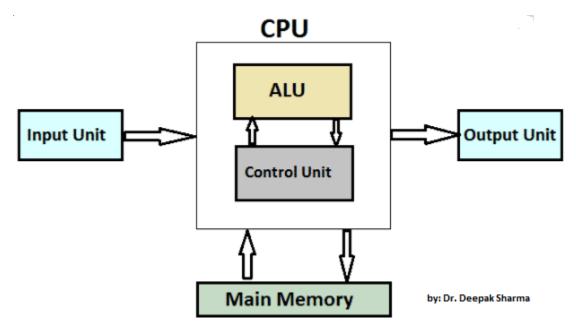

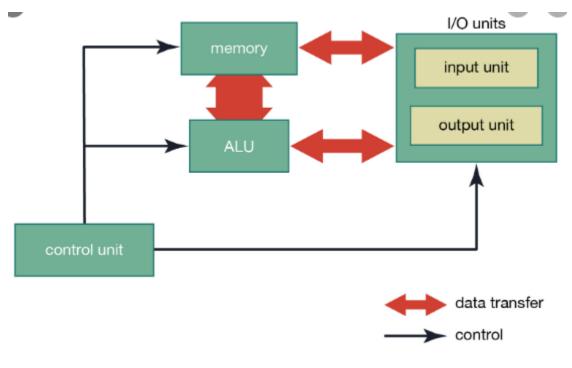

The processor's core elements are an "Arithmetic and logic unit "(ALU) along with "Register Set", and then a "control unit (CU)". The ALU operates the real data analysis or computing. The "control unit" governs data and instructions navigate within the processor and handles ALU operation. The Register Collection contains intermediate data using in instruction execution.

## 1.1 ALU (Arithmetic Logic Unit):

An "arithmetic logic unit (ALU)" is an advanced circuit utilized for certain manipulations of arithmetic's and logic. This describes a PC's "central processing unit (CPU)"'s basic structure square. The ALU does the genuine estimation or information arrangement process. The "control unit "screens the improvement of data and rules inside and outside the processor, and manages the undertaking of the processor. CPUs of the modern day include remarkably incredible and nuanced ALUs. Present CPUs, despite ALUs, have a "control unit". A big bit of a CPU's exercises is conducted by at a certain rate one ALU, which loads data from input registers. An ALU performs operations of the arithmetic and logic.

## 1.2 CU:

A "control unit" or CU is a circuit which directs operations inside the processor of a computer. It helps the logic unit, memory, and both the input and output devices of the computer pay enough attention to instructions obtained from a program. Examples of control units used include CPUs and GPUs.

"Control unit "is responsible to collect Input data which is translated into control flags which are transferred to the central processor shortly afterwards. At that point, the processor educates the associated hardware about next procedure. Due to the variation in architecture between various manufacturers, the duties which a "control unit "performs depend on the type of CPU.)

(Fig: CU)

## 1.3 REGISTER ORGANISATION

A PC framework utilizes a progressive structure for the memory. At higher progressive levels, memory is snappier, littler, and costlier (per bit). There is an assortment of registers inside the processor that serve in the chain of command as a memory level far above principle memory just as the reserve. In the processor the registers play two capacities:

**User-visible registers:** Allow the software engineer in the machine-or low level computing construct to diminish the principle memory references by enhancing register utilization.

**Control and status registers:** Being utilized by "control unit "to screen processor activity and advantaged OS projects to screen program execution.

**1.3.1 User-Visible Registers:** A user-visible register is one which can be gotten to by the machine language performed by the processor. These can be depicted in the accompanying classifications:

• General purpose

• Data

Address

Condition codes

General-purpose registers.

The developer can be given various capacities to these registers. Frequently their utilization is actually comparable to the activity inside the guidance set. This is, for any opcode, any universally useful register can include the operand. It incorporates precise utilization of the Register for general purposes. Skimming point and stack tasks can have committed registers. Broadly useful registers could be utilized in certain

circumstances to speak to capacities (e.g., roundabout register, relocation).

**Data registers** must be utilized to store information, and can't be utilized to gauge an operand address.

**Address registers** itself in might be very universally useful, or might be devoted to a specific "addressing mode".

**Segment pointers:** A segment register contains the location of the fragment base on a machine by means of divided tending to.

**Index registers:** These are being utilized for recorded tending to, which can be filed consequently.

**Stack pointer:** If client obvious stack tending to exists then there is regularly a devoted register highlighting the TOS.

1.3.2 Control and Status Registers:

There appear to be a wide scope of processor registers being utilized handles the processor's activity. The vast majority of these are not noticeable to the client, on most machines. A couple of them might be noticeable in a control or working framework mode to machine guidelines. Four registers are required for the execution of directions.

• Program counter (PC): reserves the address of a receivable instruction

• Instruction register (IR): reserves the most recently received instructions

• Memory address registers (MAR): reserves the address of a location in memory

• Memory buffer register (MBR): reserves a word of data to be committed to memory.